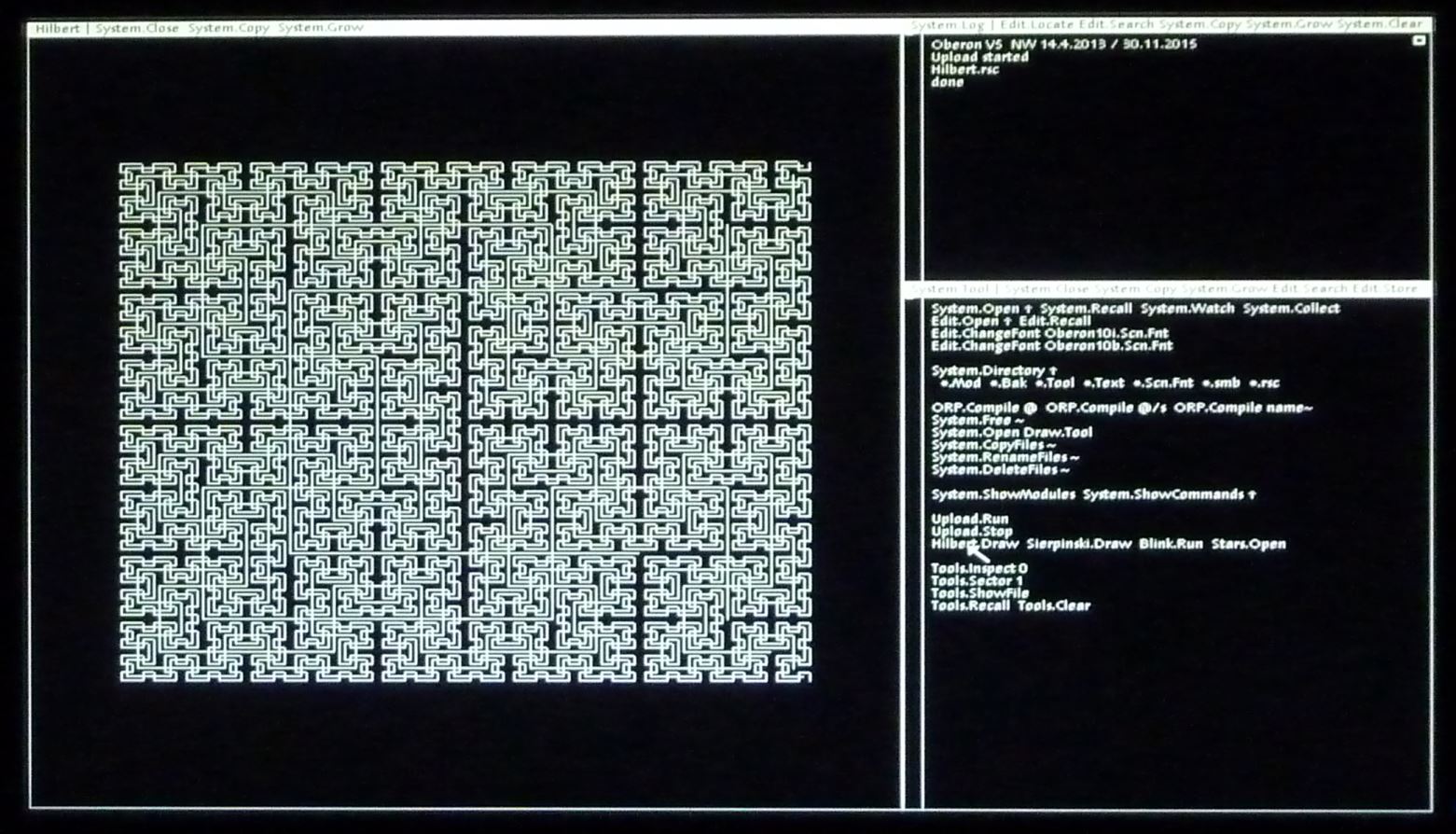

Project Oberon FPGA RISC5 Workstation

SDHC Disk Image and Verilog files for Artix A7-100T Development Boards

Introduction

The Project Oberon Workstation operating system is described in an article titled Oberon System Implemented on a Low-Cost FPGA Board which was published in Issue 91, Second Quarter 2015, of Xilinx's Xcell Journal.

It is also documented in detail in the book Project Oberon - The Design of an Operating System, a Compiler, and a Computer. Revised Edition 2013 Niklaus Wirth Jürg Gutknecht. ISBN 0-201-54428-8

We distribute the Oberon compiler, executable and source code files of the Project Oberon operating system on an SDHC disk image for no charge for those who want to use the Project Oberon Workstation on currently available FPGA development boards and off-the-shelf modules 'out-of-the-box'.

The Oberon Workstation was originally designed to be used on FPGA development boards equipped with 1 MB of static RAM which are no longer available. Unfortunately, most newer boards use DRAM memory which is much more difficult to interface, requiring circuits for refresh and initialization (calibration). The resulting Verilog code can be as complex as the entire RISC5 processor with SRAM.

A simpler alternative is to use internal BRAM (block RAM) which resides on the FPGA chip itself. Relatively low-cost FPGA boards are now available with sufficient BRAM to run the Project Oberon workstation without any external RAM. We have implemented it on two such development boards from Digilent which use the Xilinx Artix-7 100T FPGA:

Once you have installed the image on an SDHC card you can use it to boot and run the Project Oberon workstation system on one of these FPGA development boards which you have programmed with an Artix-7 FPGA bitstream file which we also supply.Oberon software development can then be carried out using Project Oberon's screen editing and compilation features without using Astrobe, Windows or any other operating system.

NOTE: The BRAM available on the Artix-7 100T device is limited to 512 KB (instead of the usual 1 MB used by Project Oberon workstation). This did present some challenges but proved to be sufficient to use the system to compile itself and all of the standard Project Oberon workstation modules.

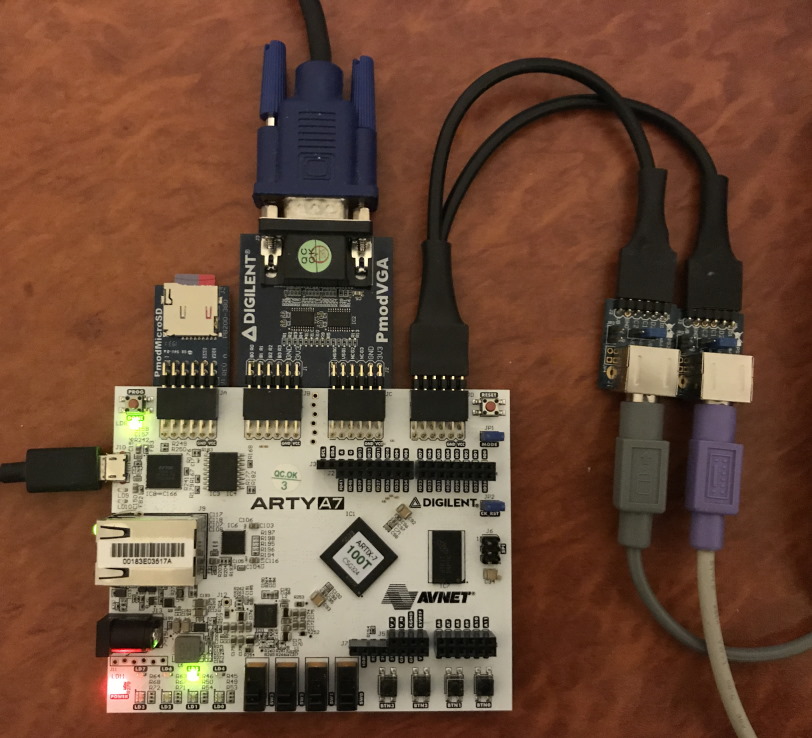

Arty A7

The Arty A7-100T board is connected to the VGA display, SDHC card, PS/2 mouse and keyboard using standard Digilent Pmod expansion modules as shown in the photo above.

| Peripheral | Digilent Pmod Module |

|---|---|

| 1024 x 768 @ 70Hz VGA display | VGA: Video Graphics Array |

| SDHC Card | MicroSD: microSD Card Slot |

| PS/2 3-button Mouse | PS2: Keyboard / Mouse Connector |

| PS/2 Keyboard | PS2: Keyboard / Mouse Connector |

The two PS/2 modules share a single Pmod socket using a 2x6-pin to Dual 6-pin Pmod Splitter Cable.

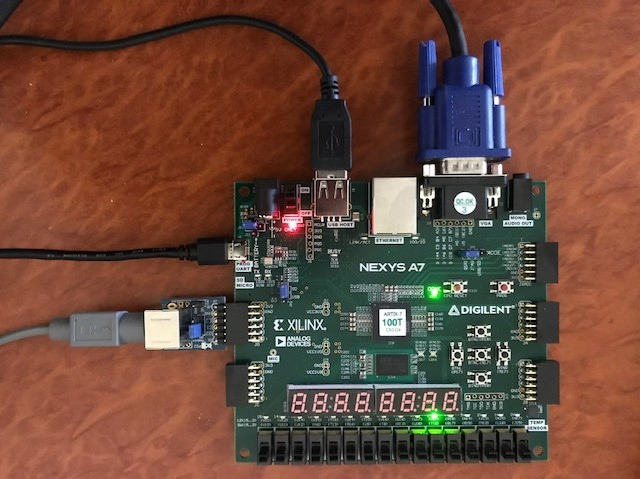

Nexys A7

The Nexys A7 board is connected to a 1024 x 768 @ 70Hz VGA display, a PC keyboard connected via the USB HID socket, and a 3-button PS/2 mouse via a Digilent PS/2 Pmod adapter. The SDHC card is inserted into the microSD socket under the board. A PS/2 keyboard could be used with an additional Pmod adapter or swapped with a 3-button USB mouse. It would only be necessary to change a few lines in the constraints file and regenerate the FPGA 'bitstream' file to do this.

Embedded Project Oberon

An alternative approach for developing Oberon software to target the RISC5 processor is to use Astrobe for FPGA RISC5, a free Windows development system that developers can use to edit and cross-compile Oberon applications. The compiled applications produced by Astrobe can be uploaded to the host FPGA RISC5 target development board via a fast RS232 link from the PC to run on a subset of Project Oberon 2013.Go to the Embedded Project Oberon page for more information .

Comparison with Standard Project Oberon

The Oberon language source code that was used to build the Project Oberon system, compiler and applications can be found on the official Project Oberon site. The latest update date of any of the source code files is 9.3.2020 (ORB.Mod)

The only change made to any of the Oberon source code files was a single additional statement in Modules.Free to allow more efficient use of the available modules space whenever the most recently loaded module is unloaded. This should minimise the occurrence of "insufficient space" errors when attempting to run a command of a module that is not already loaded.

The differences between the implementation of Project Oberon on the A7-100T boards and the standard Project Oberon workstation system are:

| Standard | Nexys A7-100T | Arty A7-100T | |

|---|---|---|---|

| Clock | 25 MHz | 37.5 MHz | 37.5 MHz |

| VGA Display | Monochrome 1280 x 768 |

Monochrome 1280 x 768 |

Monochrome 1280 x 768 |

| Global Data + Code + Stack Data |

512 KB | 264 KB | 264 KB |

| Video RAM | 96 KB | 96 KB | 96 KB |

| Dynamic Data | 415 KB | 150 KB | 150 KB |

| GPIO | 8 | 8 | 8 |

| SPI | 2 | 2 | 2 |

| LEDs | 8 | 8 | 8 |

| Buttons | 4 | 4 | 4 |

| Switches | 8 | 8 | 4 |

| SDHC Boot | Y | Y | Y |

| RS232 Boot | Y | N | N |

The FPGA bitstream file was generated using Version 2020.2 of Xilinx's Vivado Design Suite. Changes to the Verilog sources from the originals are are:

| Module | No of lines

changed |

Description |

|---|---|---|

| RAM.v | 91 | New module to use BRAM instead of SRAM. This is based on

the original written by Magnus Karlsson of Saanlima Electronics. |

| RISC5Top.v | 35 | External pixel clock, faster clock speed, no SRAM etc. |

| VID.v | 5 | Pixel clock generation |

| RS232R.v | 1 | Faster clock speed |

| RS232T.v | 1 | Faster clock speed |

| SPI.v | 1 | Faster clock speed |

Downloads

The complete Project Oberon FPGA RISC5 Workstation software system consists of:

- A MicroSDHC disk image file containing the Project Oberon OS with sources

- A bitstream file to program the RISC5 processor on the target FPGA processor

- Verilog sources to customise the RISC5 system if desired using the free WebPACK edition of Xilinx's Vivado Design Suite

WARNING: This version of Project Oberon is intended for experimental use only. Because applications only have access to half of the RAM that the system was originally designed to have, system failures due to attempts to use more RAM than is available are more likely to occur. The System.Watch command can be used to check memory availability and System.Free can be used to regain memory from modules that had been loaded in the current session but are no longer required.

Request your copy free of charge via download here.

Technical Support

If you have any questions about this system ask them on the Astrobe for FPGA RISC5 Forum. You will also find the latest news and implementation details there.